进行阻塞I/O操作时需要cpu资源调度引发的思考

我们知道,在多线程开发环境下,倘若某线程正在进行阻塞I/O操作时,cpu往往会将时间片分配给其他线程,而不是死等io操作完成,这大大增加了CPU利用率。但这只是表面的东西,我们也要知道操作系统是通过什么方式来完成这种高效的调度模式的。

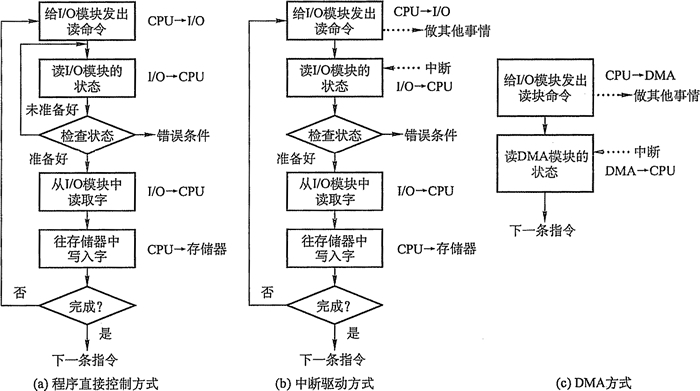

首先我们需要了解控制设备和内存或处理机之间的数据传送,外围设备和内存之间的四种I/O方式:

程序直接控制方式

如图5-1(a)所示,计算机从外部设备读取数据到存储器,每次读一个字的数据。对读入的每个字,CPU需要对外设状态进行循环检查,直到确定该字已经在I/O控制器的数据寄存器中。在程序直接控制方式中,由于CPU的高速性和I/O设备的低速性,致使CPU的绝大部分时间都处于等待I/O设备完成数据I/O的循环测试中,造成了 CPU资源的极大浪费。在该方式中,CPU之所以要不断地测试I/O设备的状态,就是因为在CPU中没有釆用中断机构,使I/O设备无法向CPU报告它已完成了一个字符的输入操作。

程序直接控制方式虽然简单易于实现,但是其缺点也是显而易见的,由于cpu和I/O设备只能串行工作,导致CPU的利用率相当低。

- 中断驱动方式

中断驱动方式的思想是,允许I/O设备主动打断CPU的运行并请求服务,从而“解放”CPU,使得其向I/O控制器发送读命令后可以继续做其他有用的工作。如图5-1(b)所示,我们从I/O控制器和CPU两个角度分别来看中断驱动方式的工作过程:

- 从I/O控制器的角度来看,I/O控制器从CPU接收一个读命令,然后从外围设备读数据。一旦数据读入到该I/O控制器的数据寄存器,便通过控制线给CPU发出一个中断信号,表示数据已准备好,然后等待CPU请求该数据。I/O控制器收到CPU发出的取数据请求后,将数据放到数据总线上,传到CPU的寄存器中。至此,本次I/O操作完成,I/O控制器又可幵始下一次I/O操作。

- 从CPU的角度来看,CPU发出读命令,然后保存当前运行程序的上下文(现场,包括程序计数器及处理机寄存器),转去执行其他程序。在每个指令周期的末尾,CPU检查中断。当有来自I/O控制器的中断时,CPU保存当前正在运行程序的上下文,转去执行中断处理程序处理该中断。这时,CPU从I/O控制器读一个字的数据传送到寄存器,并存入主存。接着, CPU恢复发出I/O命令的程序(或其他程序)的上下文,然后继续运行。

中断驱动方式比程序直接控制方式有效,但由于数据中的每个字在存储器与I/O控制器之间的传输都必须经过CPU,这就导致了中断驱动方式仍然会消耗较多的CPU时间。

- DMA方式(直接内存存取)

在中断驱动方式中,I/O设备与内存之间的数据交换必须要经过CPU中的寄存器,所以速度还是受限,而DMA(直接存储器存取)方式的基本思想是在I/O设备和内存之间开辟直接的数据交换通路,彻底“解放” CPU。DMA方式的特点是:

- 基本单位是数据块。

- 所传送的数据,是从设备直接送入内存的,或者相反。

- 仅在传送一个或多个数据块的开始和结束时,才需CPU干预,整块数据的传送是在DMA控制器的控制下完成的。

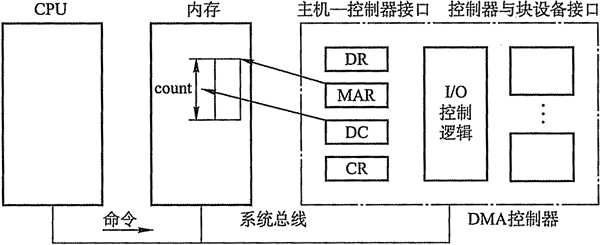

为了实现在主机与控制器之间成块数据的直接交换,必须在DMA控制器中设置如下四类寄存器:

- 命令/状态寄存器(CR):用于接收从CPU发来的I/O命令或有关控制信息,或设备的状态。

- 内存地址寄存器(MAR):在输入时,它存放把数据从设备传送到内存的起始目标地址;在输出时,它存放由内存到设备的内存源地址。

- 数据寄存器(DR):用于暂存从设备到内存,或从内存到设备的数据。

- 数据计数器(DC):存放本次CPU要读或写的字(节)数。

如图5-1(c)所示,DMA方式的工作过程是:CPU读写数据时,它给I/O控制器发出一条命令,启动DMA控制器,然后继续其他工作。之后CPU就把控制操作委托给DMA控制器,由该控制器负责处理。DMA控制器直接与存储器交互,传送整个数据块,每次传送一个字,这个过程不需要CPU参与。当传送完成后,DMA控制器发送一个中断信号给处理器。因此只有在传送开始和结束时才需要CPU的参与。

DMA控制方式与中断驱动方式的主要区别是中断驱动方式在每个数据需要传输时中断CPU,而DMA控制方式则是在所要求传送的一批数据全部传送结束时才中断CPU;此外,中断驱动方式数据传送是在中断处理时由CPU控制完成的,而DMA控制方式则是在DMA 控制器的控制下完成的。

通道控制方式

I/O通道是指专门负责输入/输出的处理机。I/O通道方式是DMA方式的发展,它可以进一步减少CPU的干预,即把对一个数据块的读(或写)为单位的干预,减少为对一组数据块的读(或写)及有关的控制和管理为单位的干预。同时,又可以实现CPU、通道和I/O设备三者的并行操作,从而更有效地提高整个系统的资源利用率。

例如,当CPU要完成一组相关的读(或写)操作及有关控制时,只需向I/O通道发送一条I/O指令,以给出其所要执行的通道程序的首地址和要访问的I/O设备,通道接到该指令后,通过执行通道程序便可完成CPU指定的I/O任务,数据传送结束时向CPU发中断请求。I/O通道与一般处理机的区别是:通道指令的类型单一,没有自己的内存,通道所执行的通道程序是放在主机的内存中的,也就是说通道与CPU共享内存。

I/O通道与DMA方式的区别是:DMA方式需要CPU来控制传输的数据块大小、传输的内存位置,而通道方式中这些信息是由通道控制的。另外,每个DMA控制器对应一台设备与内存传递数据,而一个通道可以控制多台设备与内存的数据交换。

上述这四种IO控制方式的发展使得cpu在IO操作时需要干涉的时间越来越少,大大增强了多线程情况下的并发执行能力。

接着我们讲一讲I/O的一些基本概念,让读者更加理解IO的体系:

- I/O子系统概述

由于I/O设备种类繁多,功能和传输速率差异巨大,需要多种方法来进行设备控制。这些方法共同组成了操作系统内核的I/O子系统,它将内核的其他方面从繁重的I/O设备管理中解放出来。I/O核心子系统提供的服务主要有I/O调度、缓冲与高速缓存、设备分配与回收、假脱机、设备保护和差错处理等。

- I/O调度概念

I/O调度就是确定一个好的顺序来执行这些I/O请求。应用程序所发布的系统调用的顺序不一定总是最佳选择,所以需要I/o调度来改善系统整体性能,使进程之间公平地共享设备访问,减少I/O完成所需要的平均等待时间。

操作系统开发人员通过为每个设备维护一个请求队列来实现调度。当一个应用程序执行阻塞I/O系统调用时,该请求就加到相应设备的队列上。I/O调度会重新安排队列顺序以改善系统总体效率和应用程序的平均响应时间。

I/O子系统还可以使用主存或磁盘上的存储空间的技术,如缓冲、高速缓冲、假脱机等,来改善计算机效率。

高速缓存与缓冲区

- 磁盘高速缓存(Disk Cache)

操作系统中使用磁盘高速缓存技术来提高磁盘的I/O速度,对高速缓存复制的访问要比原始数据访问更为高效。例如,正在运行的进程的指令既存储在磁盘上,也存储在物理内存上,也被复制到CPU的二级和一级高速缓存中。

不过,磁盘高速缓存技术不同于通常意义下的介于CPU与内存之间的小容量高速存储器,而是指利用内存中的存储空间来暂存从磁盘中读出的一系列盘块中的信息。因此,磁盘高速缓存在逻辑上属于磁盘,物理上则是驻留在内存中的盘块。

高速缓存在内存中分为两种形式:一种是在内存中开辟一个单独的存储空间作为磁速缓存,大小固定;另一种是把未利用的内存空间作为一个缓沖池,供请求分页系统和磁盘I/O时共享。

- 缓冲区(Buffer)

在设备管理子系统中,引入缓冲区的目的主要有:

- 缓和CPU与I/O设备间速度不匹配的矛盾。

- 减少对CPU的中断频率,放宽对CPU中断响应时间的限制。

- 解决基本数据单元大小(即数据粒度)不匹配的问题。

- 提高CPU和I/O设备之间的并行性。